Xilinx ISE 原理图如何修改模块引脚位置?

来源:网络收集 点击: 时间:2024-04-28【导读】:

讲解使用Xilinx ISE原理图编辑时,引用自己编写的模块时,对于引脚位置不满意的解决办法。讲解Symbol Wizard工具的用法。工具/原料moreXilinx 14.7方法/步骤1/9分步阅读 2/9

2/9 3/9

3/9 4/9

4/9 5/9

5/9 6/9

6/9 7/9

7/9 8/9

8/9 9/9

9/9 注意事项

注意事项

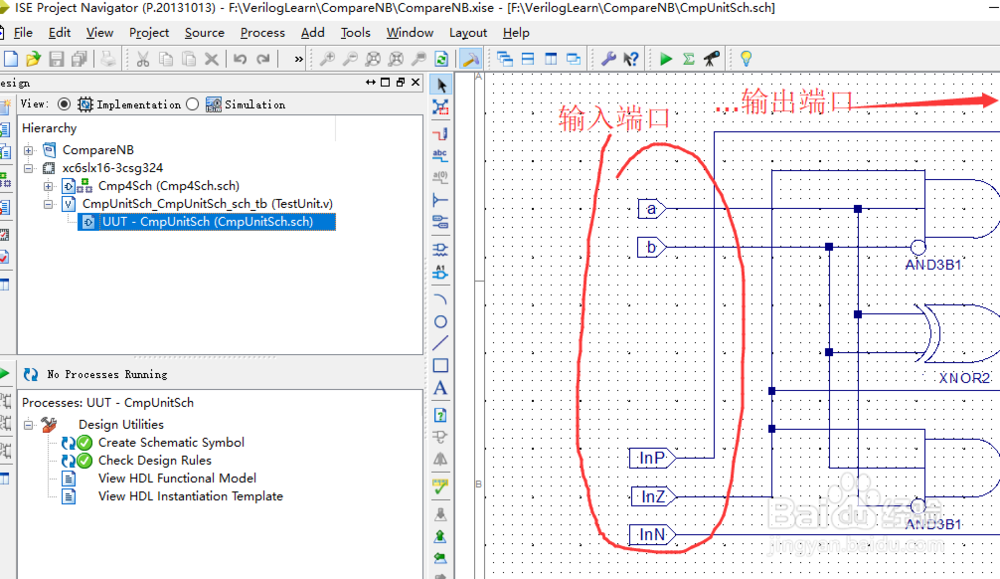

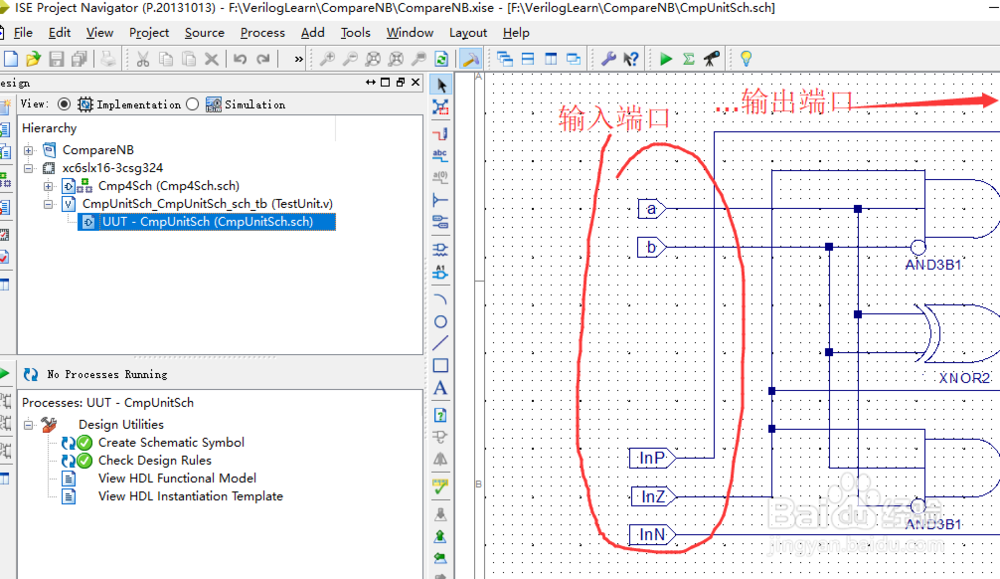

如图,我们有一个sch文件(原理图输入方式的模块),如图,我们有一些输入端口和输出端口。

2/9

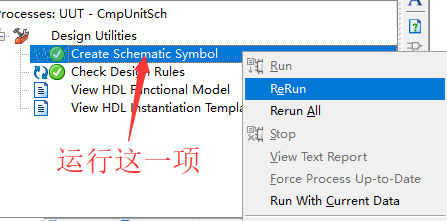

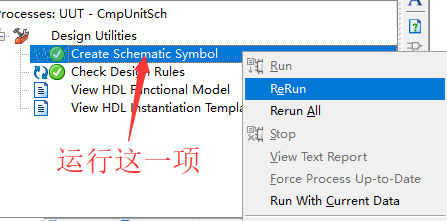

2/9选中该sch文件,在下面Processes列表中,右键运行Create Schematic Symbol。运行这一步后才可以在原理图编辑中被调用。

3/9

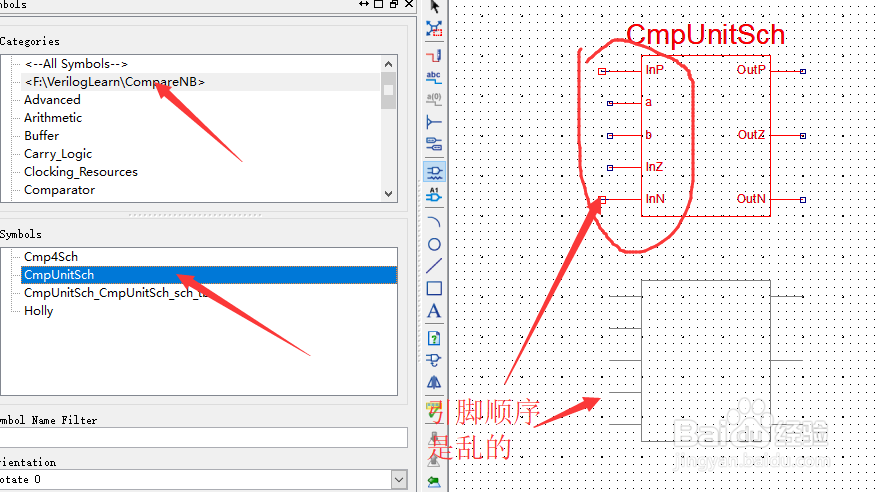

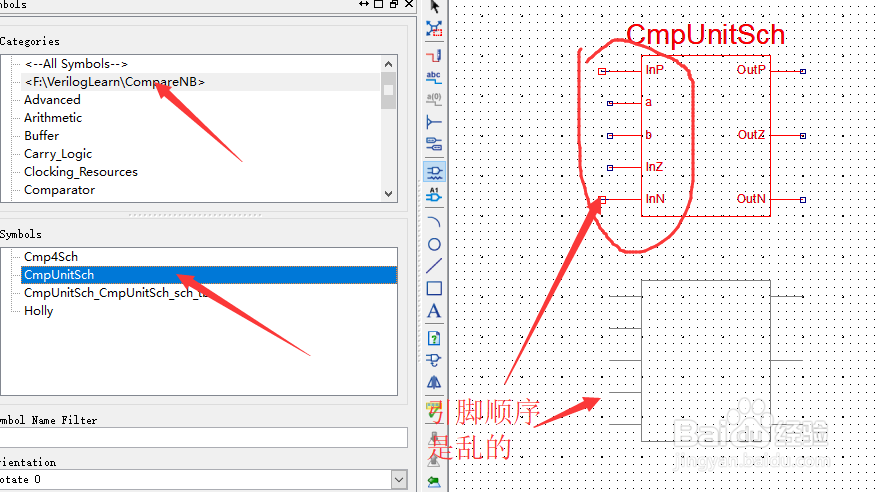

3/9新建sch文件,使用此模块,生成的模块Symbol长相如图。和想象中的端口位置并不一致。

4/9

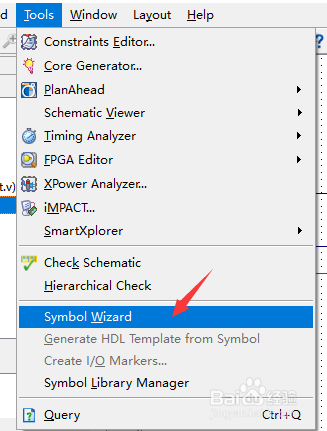

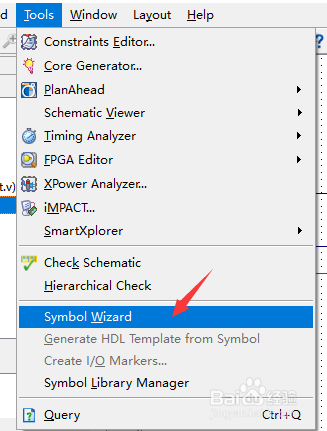

4/9在Tools菜单点击Symbol Wizard菜单,打开Symbol Wizard窗口。

5/9

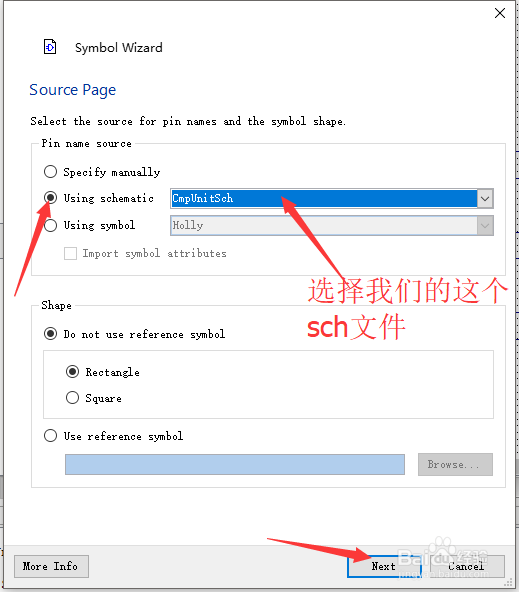

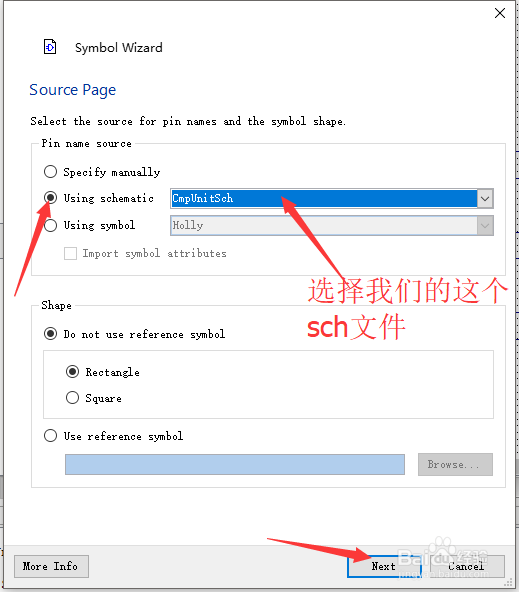

5/9选择Using schematic,选择之前那个模块的sch文件。

6/9

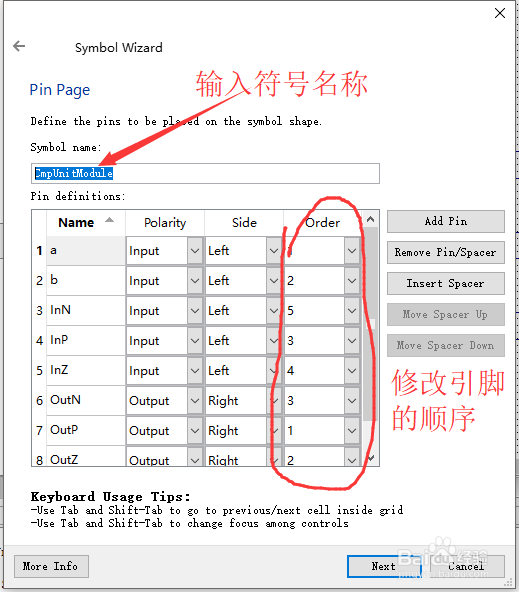

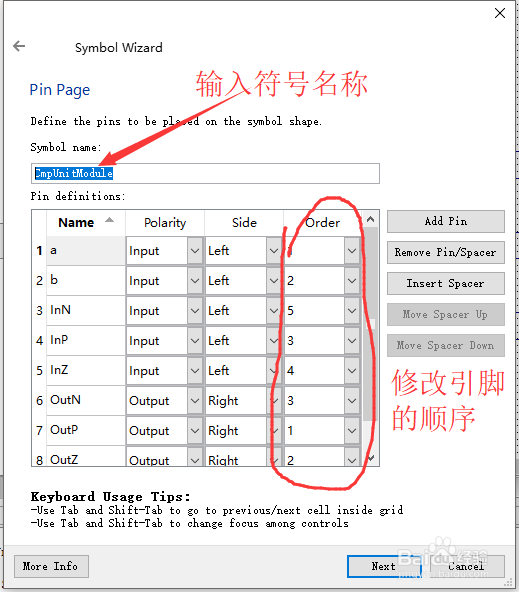

6/9接着点击Next,然后输入Symbol name,也可以使用默认名称

7/9

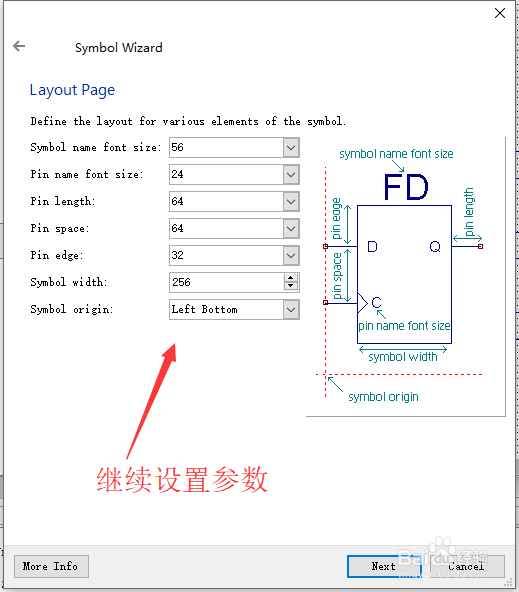

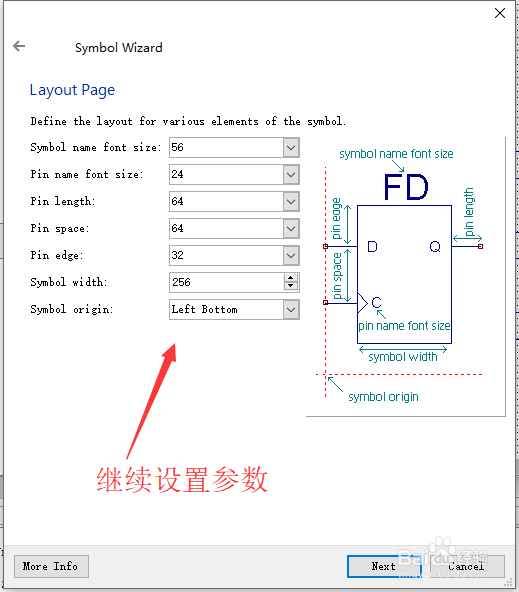

7/9点击Next,接着设置距离,长度,显示样式等信息。然后再Order栏下修改引脚顺序。

8/9

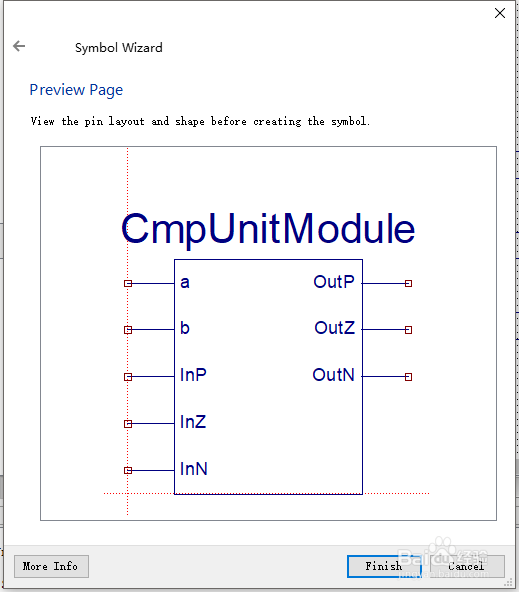

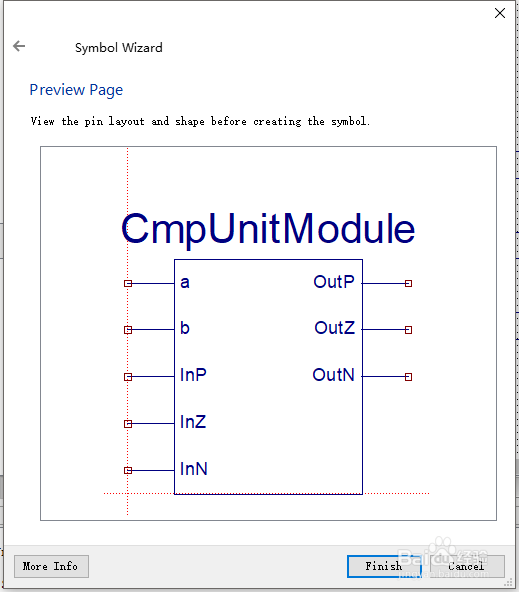

8/9继续点击Next来到预览窗口,可以看到预览效果。如果不满意可以回到以前的步骤调整。

9/9

9/9然后回到原理图编辑,Symbol列表里面就有我们刚才创建的Symbol了。

注意事项

注意事项Symbol Wizard有bug, 使用默认Symbol名称可能无法被更新。如果遇到这种情况重启软件即可。

XILINX版权声明:

1、本文系转载,版权归原作者所有,旨在传递信息,不代表看本站的观点和立场。

2、本站仅提供信息发布平台,不承担相关法律责任。

3、若侵犯您的版权或隐私,请联系本站管理员删除。

4、文章链接:http://www.1haoku.cn/art_615647.html

订阅

订阅