VHDL数控分频器编程

来源:网络收集 点击: 时间:2024-04-29LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY speaker IS

PORT(clk:IN STD_LOGIC;

tone:IN STD_LOGIC_VECTOR (11 DOWNTO 0);

spk:OUT STD_LOGIC);

END ENTITY speaker;

ARCHITECTURE one OF speaker IS

SIGNAL preclk:STD_LOGIC;

SIGNAL fullspk:STD_LOGIC;

BEGIN

---------------------

divclk:PROCESS(clk)

VARIABLE Count8:STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

IF (clkEVENT AND clk=1) THEN

IF Count87 THEN preclk=NOT preclk;Count8:=0000;

ELSE Count8:=Count8+1;

END IF;

END IF;

END PROCESS divclk;

----------------------

genspk:PROCESS(preclk,tone)

VARIABLE Count12:STD_LOGIC_VECTOR(11 DOWNTO 0);

BEGIN

IF (preclkEVENT AND preclk=1) THEN

IF Count12=16#FFF# THEN Count12:=tone;fullspk=1;

ELSE Count12:=Count12+1;fullspk=0;

END IF;

END IF;

END PROCESS genspk;

----------------------

delayspk:PROCESS (fullspk)

VARIABLE Count2:STD_LOGIC;

BEGIN

IF (fullspkEVENT AND fullspk=1) THEN Count2:=NOT Count2;

IF Count2=1 THEN spk =1;

ELSE spk=0;

END IF;

END IF;

END PROCESS delayspk;

END ARCHITECTURE one;

2/3

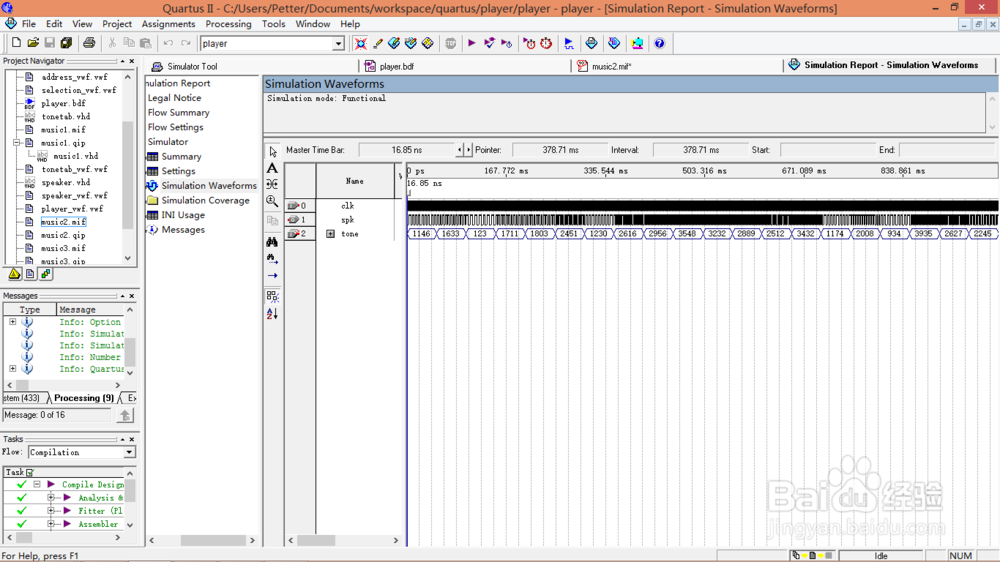

2/3进行波形仿真

3/3

3/3说明:

tone即是分频系数

spk既是产生的信号

编程版权声明:

1、本文系转载,版权归原作者所有,旨在传递信息,不代表看本站的观点和立场。

2、本站仅提供信息发布平台,不承担相关法律责任。

3、若侵犯您的版权或隐私,请联系本站管理员删除。

4、文章链接:http://www.1haoku.cn/art_625981.html

订阅

订阅