msp430F123利用端口输出系统时钟

来源:网络收集 点击: 时间:2024-02-18msp430F123芯片存召捕在多种系统时钟和管脚复用。利用这个特定可实现较多功能。P1.4脚是GPIO/TCK/SMCLK复用的。

2/7

2/7从管脚定义它可以做GPIO也可以JTAG还能输出SMCK时钟,这里通过设置P1.4的SMCLK实现时钟频率输出。

3/7

3/7新建一个工程,

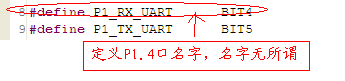

定义端口名字

4/7

4/7P1DIR =P1_RX_UART ; 设置为输出

P1SEL =P1_RX_UART ; 利用P1SEL选通P1.4的第二功能

从P1.4输出

5/7

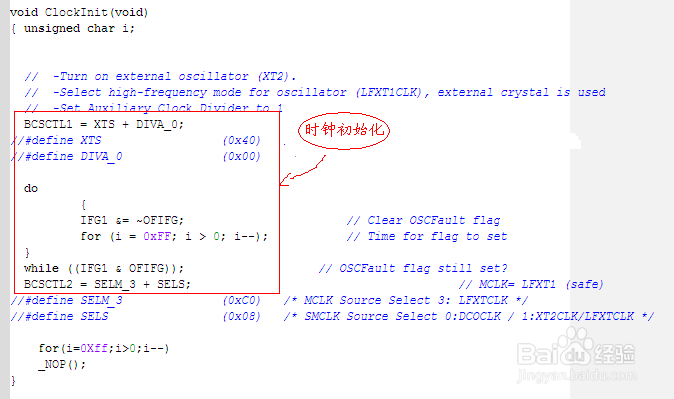

5/7初始化设置系统时钟

void ClockInit(void)

{ unsigned char i;

BCSCTL1 = XTS + DIVA_0;

//#define XTS (0x40) /* LFXTCLK 0:Low Freq. / 1: High Freq. */

//#define DIVA_0 (0x00) /* ACLK Divider 0: /1 */

do

{

IFG1 = ~OFIFG; // Clear OSCFault flag

for (i = 0xFF; i 0; i--); // Time for flag to set

}

while ((IFG1 OFIFG)); // OSCFault flag still set?

BCSCTL2 = SELM_3 + SELS;// MCLK= LFXT1 (safe)

//#define SELM_3 (0xC0) /* MCLK Source Select 3: LFXTCLK */

//#define SELS 付芬 (0x08) /* SMCLK Source Select 0:DCOCLK / 1:XT2CLK/LFXTCLK */

for(i=0Xff;i0;i--)

_NOP();

}

6/7

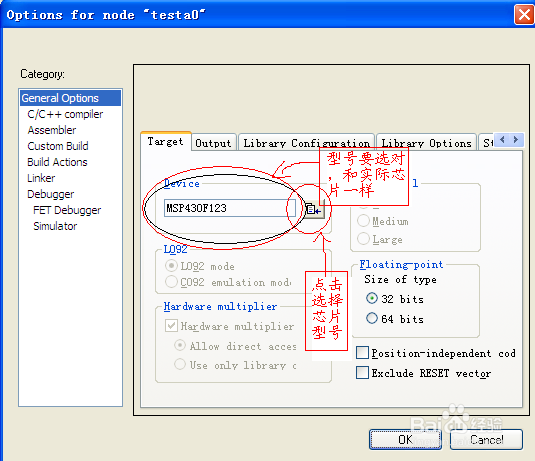

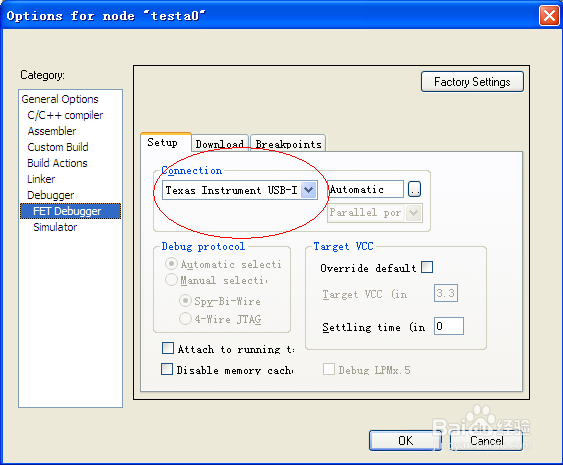

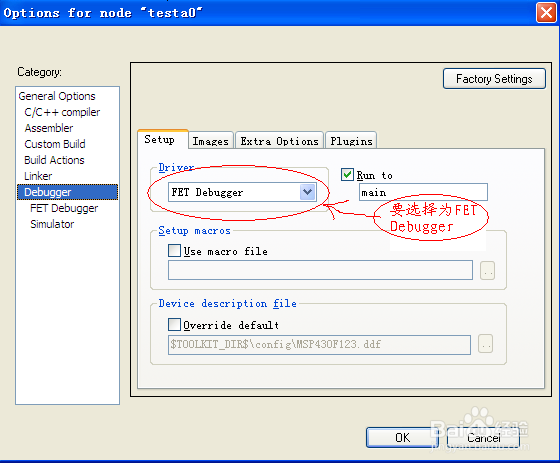

6/7对工程设置以下几个地方

1) FETDebugger --setup--connection选择 USB连接方式

2)Debugger下的--setuo--Driver 选 FET Debugger

3) General Options --Target -- Device --争惹获点按钮选 MSP430F123

7/7

7/7运行,然后用示波器测量 P1.4端口,观察波形。

注意事项USB写入器:msp-fet430uif要设对;

P1SEL P1DIR要设对。

硬件MSP430FSMCLK版权声明:

1、本文系转载,版权归原作者所有,旨在传递信息,不代表看本站的观点和立场。

2、本站仅提供信息发布平台,不承担相关法律责任。

3、若侵犯您的版权或隐私,请联系本站管理员删除。

4、文章链接:http://www.1haoku.cn/art_67411.html

订阅

订阅