cadence16.6 学习066-PCB中设置T型等长规则

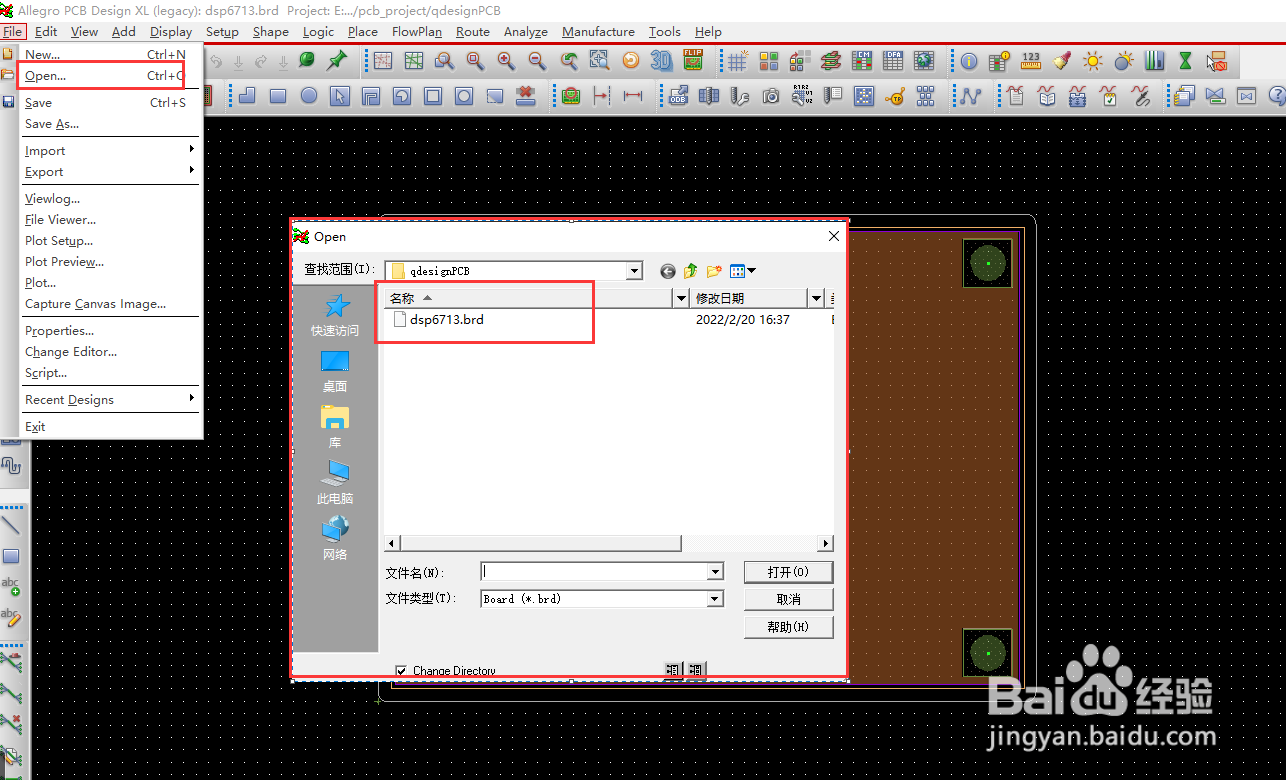

来源:网络收集 点击: 时间:2024-05-18第一步,打开PCB editor设计软件,打开对应的PCB工程;

2/8

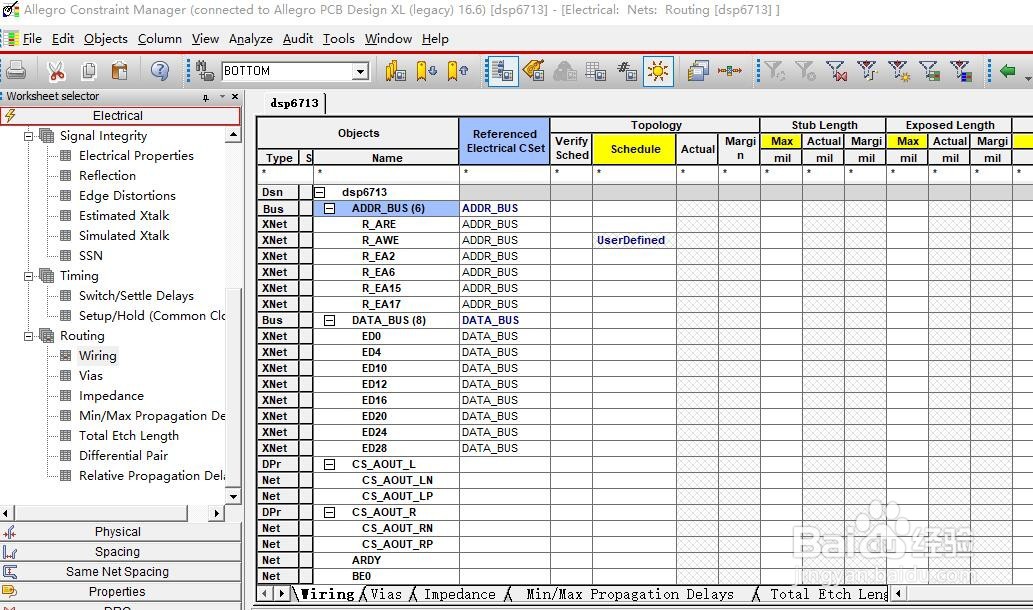

2/8第二步,打开约束管理器,将之前设置好的T型网络选中,右键Create-bus;

3/8

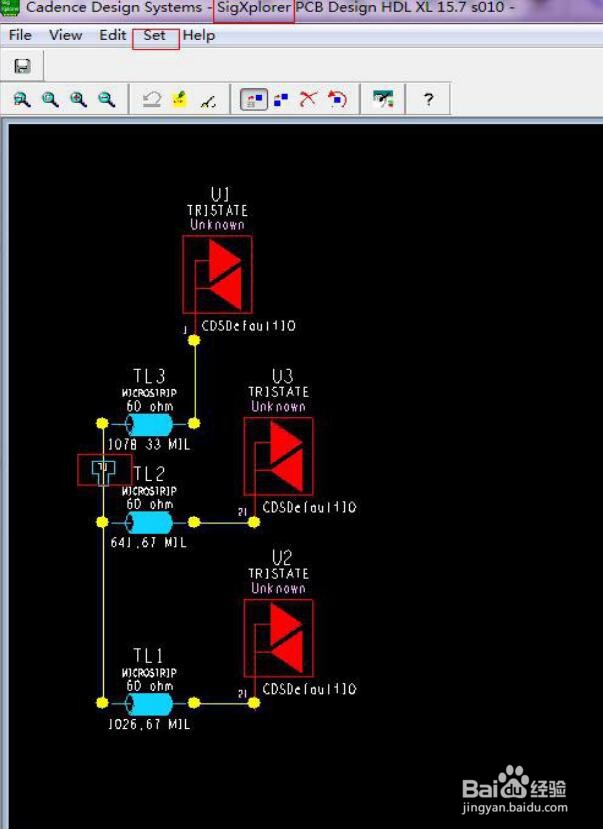

3/8第三步,选中创建的BUS,右键sigxplorer,

4/8

4/8第四步,可以看到刚才的拓扑结构,单击setup-constraints子菜单,选中rel-prep-delay面板;

5/8

5/8第五步,创建两个约束,这里注意设置的是从T1到U2和T1到U3,即是U2和U3之间的T型等长,约束名称是一样的,范围scope选中local.

6/8

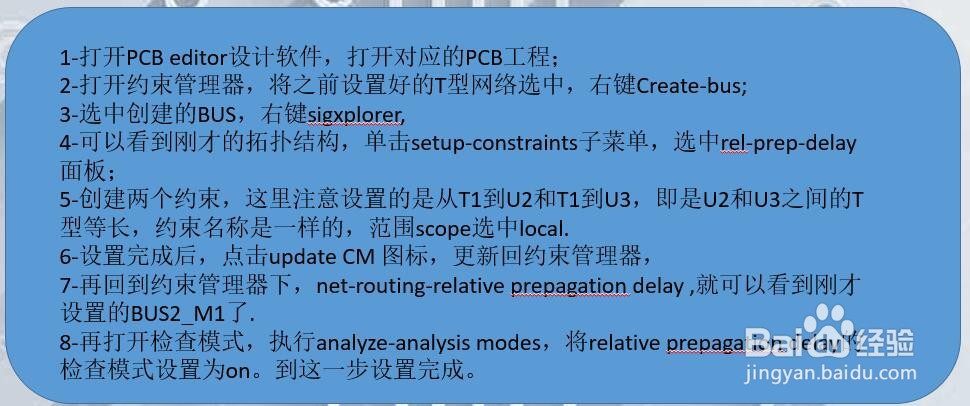

6/8第六步,设置完成后,点击update CM 图标,更新回约束管理器,

7/8

7/8第七步,再回到约束管理器下,net-routing-relative prepagation delay ,就可以看到刚才设置的BUS2_M1了.

8/8

8/8第八步,再打开检查模式,执行analyze-analysis modes,将relative prepagation delay的检查模式设置为on。设置完成。

总结1/1

总结1/11-打开PCB editor设计软件,打开对应的PCB工程;

2-打开约束管理器,将之前设置好的T型网络选中,右键Create-bus;

3-选中创建的BUS,右键sigxplorer,

4-可以看到刚才的拓扑结构,单击setup-constraints子菜单,选中rel-prep-delay面板;

5-创建两个约束,这里注意设置的是从T1到U2和T1到U3,即是U2和U3之间的T型等长,约束名称是一样的,范围scope选中local.

6-设置完成后,点击update CM 图标,更新回约束管理器,

7-再回到约束管理器下,net-routing-relative prepagation delay ,就可以看到刚才设置的BUS2_M1了.

8-再打开检查模式,执行analyze-analysis modes,将relative prepagation delay的检查模式设置为on。到这一步设置完成。

注意事项

注意事项以上是个人操作经验,仅供参考,谢谢!

版权声明:

1、本文系转载,版权归原作者所有,旨在传递信息,不代表看本站的观点和立场。

2、本站仅提供信息发布平台,不承担相关法律责任。

3、若侵犯您的版权或隐私,请联系本站管理员删除。

4、文章链接:http://www.1haoku.cn/art_794332.html

订阅

订阅