Verilog 如何编写仿真测试模块?

来源:网络收集 点击: 时间:2024-06-26首先,在项目上右键,点击New Source创建新的代码文件。

2/9

2/9选择User Document创建自定义的文本文件。文件名和后缀都随意了。

该文件用来存放仿真需要的数据,与项目本身并无关联。

3/9

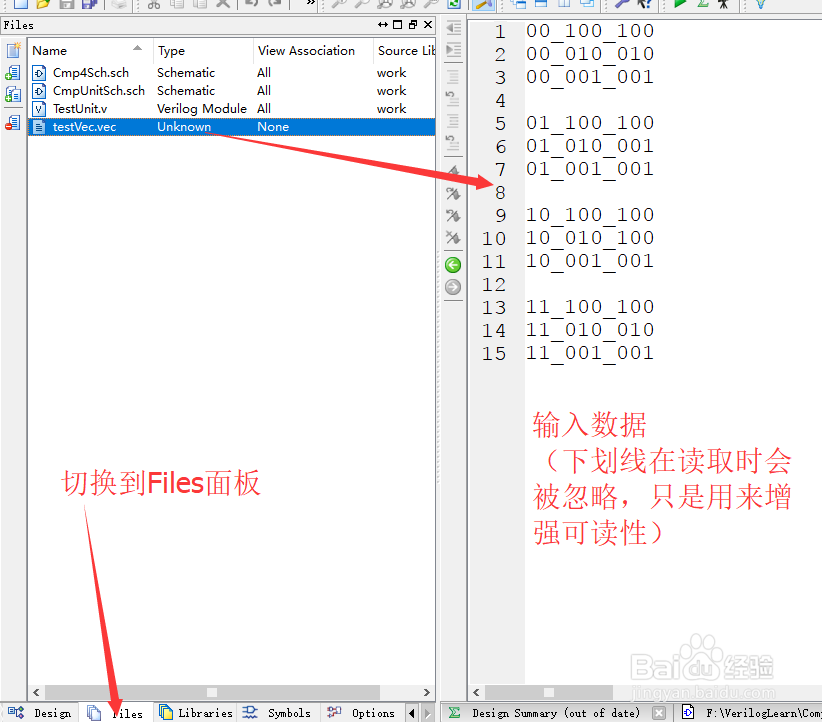

3/9创建好后,在下方切换到Files面板,双击打开该文件,按照自己喜欢的形式输入数据(可以有下划线,换行)

如图,我采用每行一组输入输出信号的形式编写文件。

4/9

4/9数据文件写好后,就要编写Verilog测试模块读取该文件并对模块进行测试了。在项目上右键,点击New Source,接着选择Verilog Test Fixture,输入文件名并继续,选择待测模块,接着创建文件。

5/9

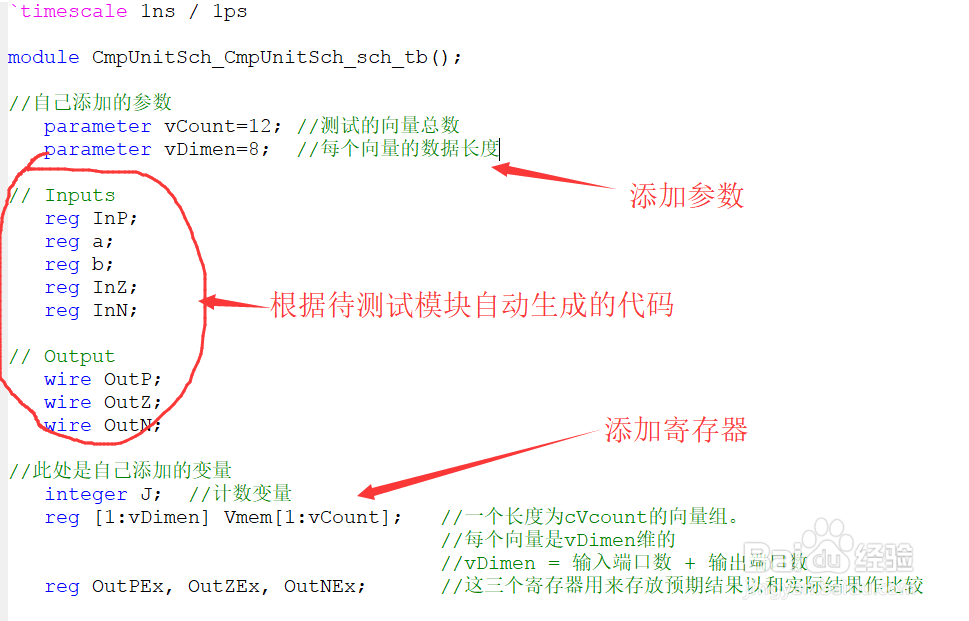

5/9双击打开该文件,我们看到待测试模块输入对应了一些reg寄存器类型,输出部分对应了一些wire类型。

我们添加两个parameter常量,接着添加计数变量J用于for循环,添加一个向量数组用于存放文件读取的数据。

6/9

6/9如图是程序自动生成的实例化和连接待测模块的代码。

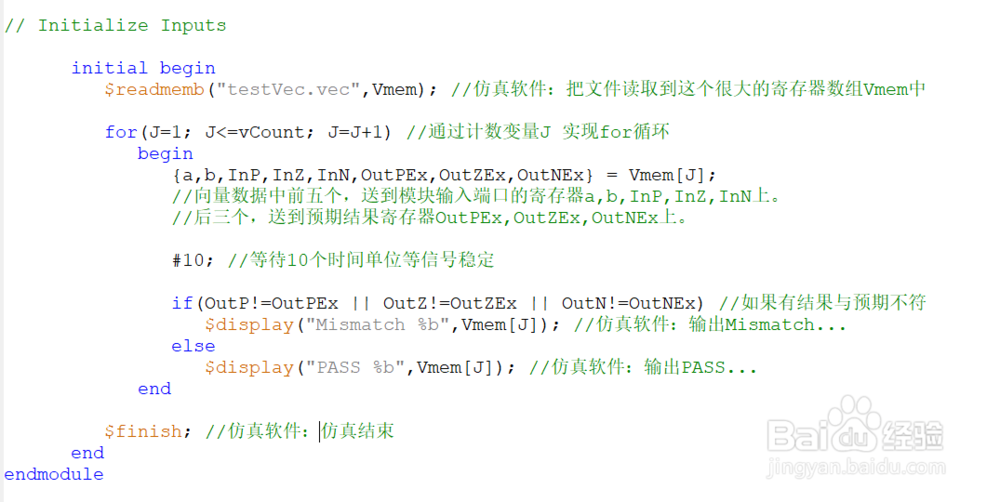

我们在下面的initial begin ... end之间编写我们的测试代码。

7/9

7/9编写思路大概如图。其中$readmemb函数从文件读取数据到Vmem数组。

$display可以在仿真软件中输出文字。

#10表示等待10个时间单位,等信号稳定

8/9

8/9在仿真模式下运行仿真,效果如图。

9/9

9/9下方控制台输出了由$display函数指定的信息。

注意事项

注意事项存放测试数据的文件和项目无关联,甚至可以是桌面上的txt. 由$readmemb函数指文件才可读取数据。

XILINXVERILOG仿真硬件描述语言版权声明:

1、本文系转载,版权归原作者所有,旨在传递信息,不代表看本站的观点和立场。

2、本站仅提供信息发布平台,不承担相关法律责任。

3、若侵犯您的版权或隐私,请联系本站管理员删除。

4、文章链接:http://www.1haoku.cn/art_917229.html

订阅

订阅