4位乘法器实验报告

来源:网络收集 点击: 时间:2024-04-07【导读】:

今天来分享个小技术。在如今的微处理器芯片中,乘法器是进行数字信号处理的核心,同时也是微处理器中进行数据处理的关键部件,它已经是现代计算机必不可少的一部分。本文主要是在于如何运用标准硬件语言(Verilog)完成四位乘法器,以及如何做二进制相乘的运算过程。该乘法器是由四位加法器构成的以时序方式设计十六位乘法器,通过多级流水方式来实现乘法功能,并以Modelsim SE 10.1a,Quartus II 7.0 (32-Bit)软件工具进行模拟,仿真并予以显示。方法/步骤1/5分步阅读 3/5

3/5 4/5

4/5 5/5

5/5

流水线功能好比一个加工厂在创业之初,只有一间小车间及孤军奋战的老板,那么,当他接到一张订单之后,他必然忙于完成第1张订单,而没有能力去接第2张订单。这样接订单→完成订单→接订单→……是一个串行的过程。后来老板发现流水线能帮助大家节省更多的人力和金钱资源,便采用了流水线。

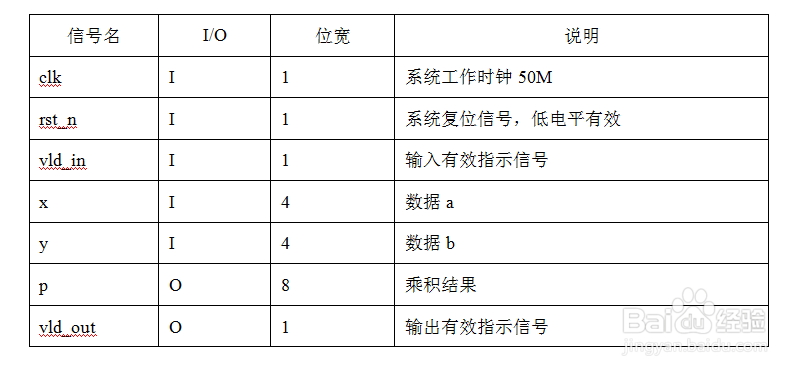

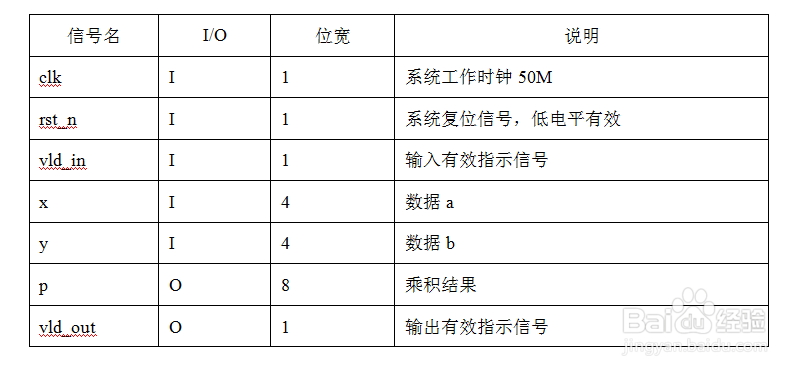

2/5简单介绍下设计模块,输入输出信号列表如下:

3/5

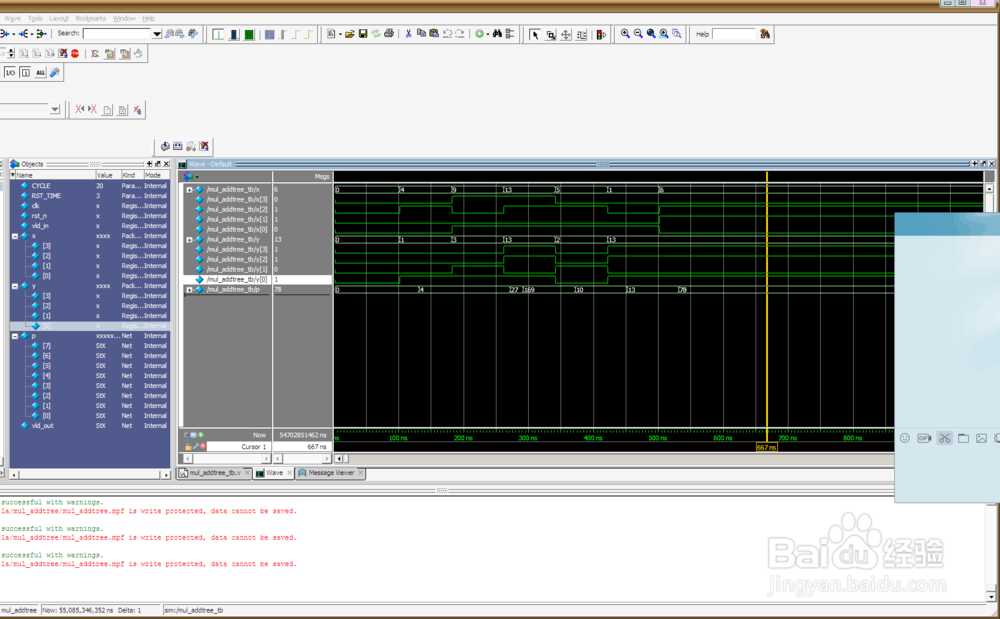

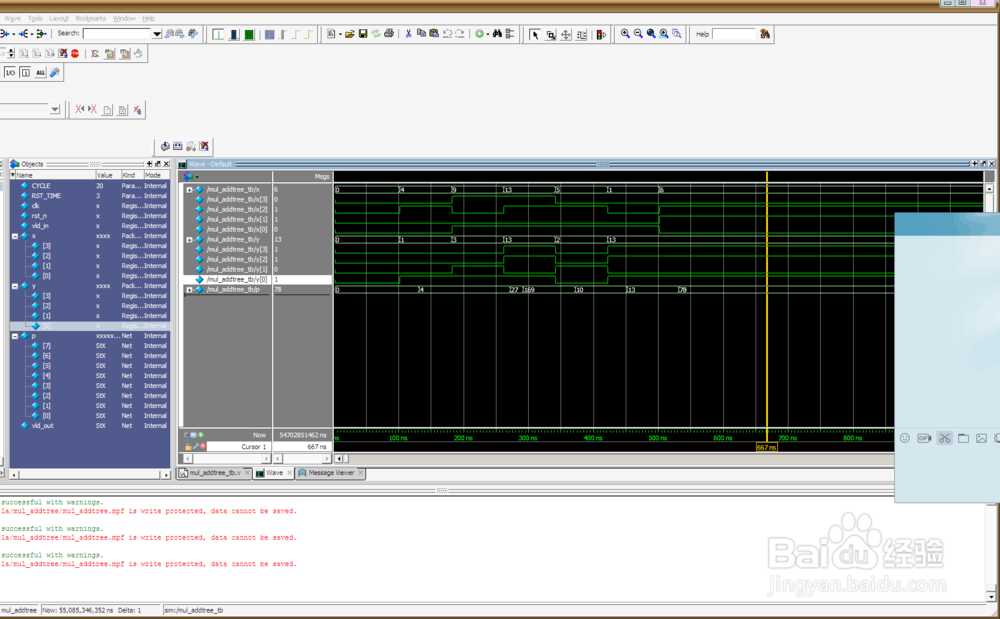

3/5在进入Modelsim SE 10.1a,创建工程,实现功能仿真,图如下。

4/5

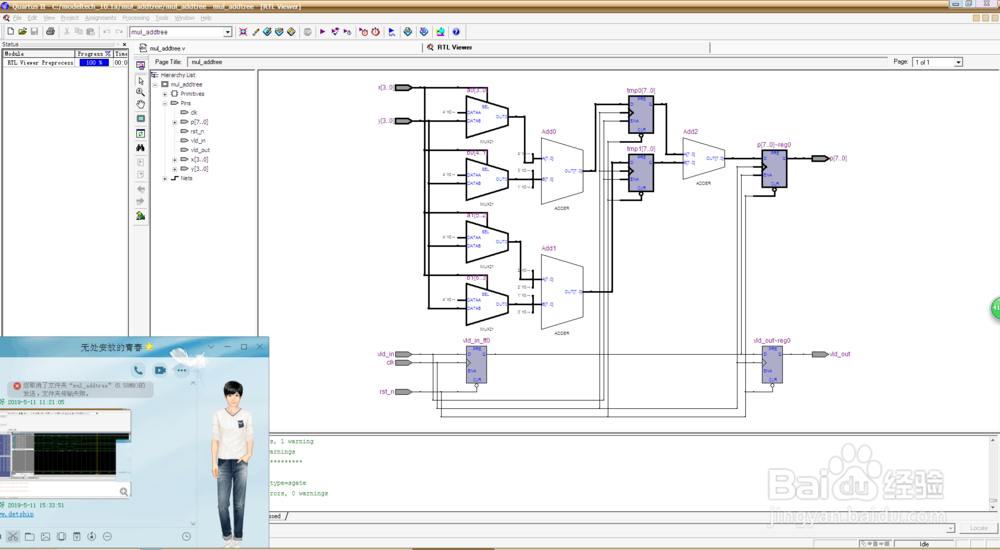

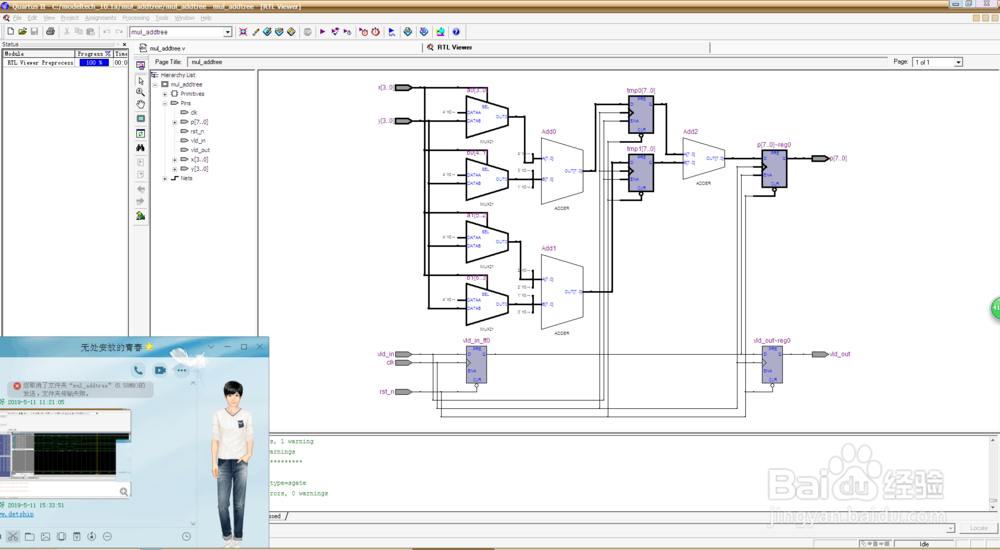

4/5在利用Quartus II 7.0 ,创建工程,编译.v文件,生成网表图。

5/5

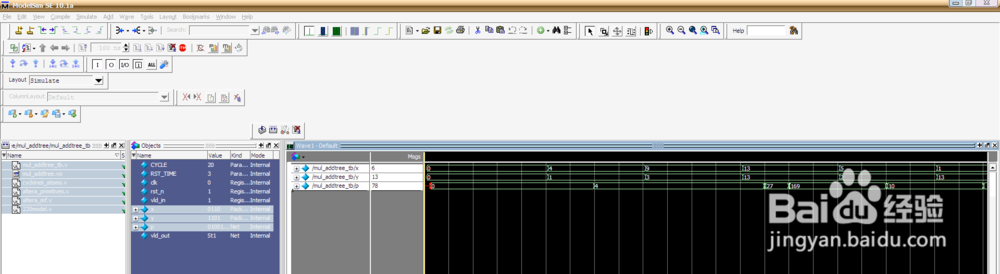

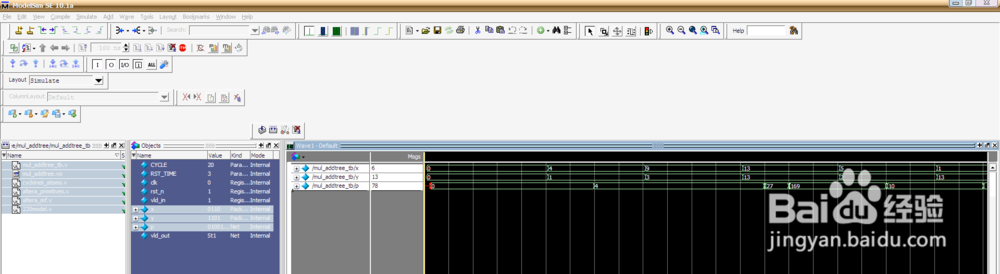

5/5因为没有专业的软件,所以要利用Quartus II 7.0 中的库文件,要用到4个。

200model.v altera_mf.v altera_primitiver.v cyclonii_atmos.v 文件,后面在进行时序仿真,得到下面的图。

版权声明:

1、本文系转载,版权归原作者所有,旨在传递信息,不代表看本站的观点和立场。

2、本站仅提供信息发布平台,不承担相关法律责任。

3、若侵犯您的版权或隐私,请联系本站管理员删除。

4、文章链接:http://www.1haoku.cn/art_460076.html

上一篇:圣光之愿礼拜堂地下室怎么去

下一篇:营养四色菜的做法

订阅

订阅